You are seeing a free-to-access but limited selection of the activity Altmetric has collected about this research output.

Click here to find out more.

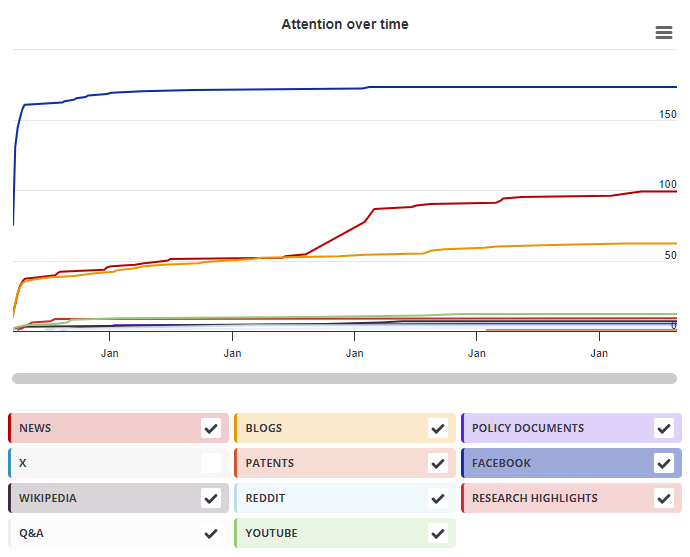

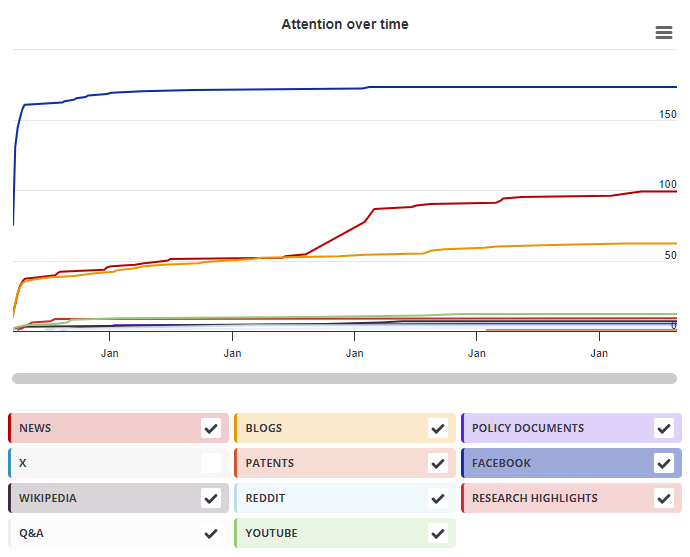

Timeline

Mendeley readers

| Title |

Digital Logic Design Using Verilog

|

|---|---|

| Published by |

Springer India, January 2016

|

| DOI | 10.1007/978-81-322-2791-5 |

| ISBNs |

978-8-13-222791-5, 978-8-13-222789-2

|

| Authors |

Vaibbhav Taraate, Taraate, Vaibbhav |

Mendeley readers

The data shown below were compiled from readership statistics for 26 Mendeley readers of this research output. Click here to see the associated Mendeley record.

Geographical breakdown

| Country | Count | As % |

|---|---|---|

| Unknown | 26 | 100% |

Demographic breakdown

| Readers by professional status | Count | As % |

|---|---|---|

| Student > Master | 5 | 19% |

| Student > Ph. D. Student | 5 | 19% |

| Student > Bachelor | 3 | 12% |

| Other | 2 | 8% |

| Student > Doctoral Student | 2 | 8% |

| Other | 5 | 19% |

| Unknown | 4 | 15% |

| Readers by discipline | Count | As % |

|---|---|---|

| Engineering | 12 | 46% |

| Computer Science | 7 | 27% |

| Unspecified | 1 | 4% |

| Materials Science | 1 | 4% |

| Design | 1 | 4% |

| Other | 0 | 0% |

| Unknown | 4 | 15% |